Visual Paradigm Desktop |

Visual Paradigm Desktop |  Visual Paradigm Online

Visual Paradigm OnlineA engenharia de sistemas depende fortemente da precisão de seus modelos. Ao usar a Linguagem de Modelagem de Sistemas (SysML), a complexidade das interações do sistema, requisitos e restrições pode crescer rapidamente se não for gerenciada com rigor. Um modelo não é meramente um desenho; é uma representação digital da realidade que impulsiona o desenvolvimento, testes e verificação. Portanto, listas de verificação de validação de modelos para revisões de arquitetura SysMLsão ferramentas essenciais para garantir a integridade.

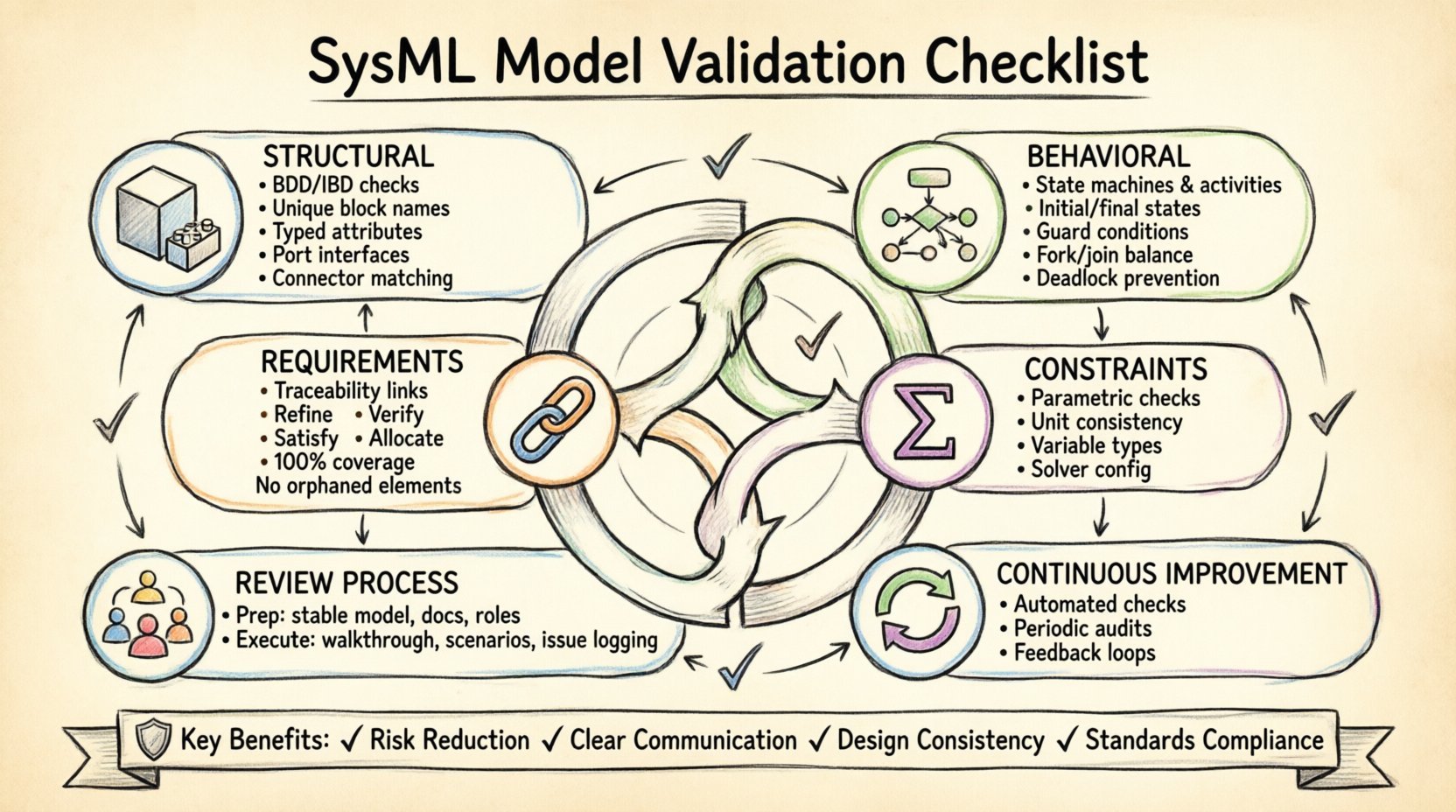

Este guia oferece uma análise aprofundada das etapas necessárias para validar um modelo SysML. Aborda a consistência estrutural, a lógica comportamental, a rastreabilidade de requisitos e a satisfação de restrições. Ao seguir esses padrões, equipes de engenharia podem reduzir riscos e melhorar a fidelidade de seus projetos arquitetônicos.

A validação na engenharia de sistemas é o processo de confirmar que o modelo representa corretamente o sistema pretendido. Diferencia-se da verificação, que pergunta se o sistema atende aos requisitos especificados. A validação pergunta se o sistema certo está sendo construído. No contexto do SysML, isso envolve verificar a sintaxe da linguagem e a semântica dos elementos do modelo.

Ao realizar uma revisão de arquitetura, o objetivo é identificar discrepâncias antes do início da geração de código ou prototipagem física. Erros detectados nesta fase são significativamente mais baratos para corrigir do que aqueles encontrados durante a fabricação ou implantação. Uma abordagem estruturada garante que nenhum elemento crítico seja negligenciado.

A base de qualquer modelo SysML reside em sua estrutura. Isso é principalmente representado em Diagramas de Definição de Blocos (BDD) e Diagramas Internos de Blocos (IBD). A validação estrutural garante que a composição física e lógica do sistema seja sólida.

Blocos representam os componentes físicos ou lógicos do sistema. Ao revisar BDDs, concentre-se no seguinte:

Os IBDs descrevem como os blocos interagem internamente. É aqui que o fluxo de matéria, energia e dados é definido.

Sistemas são dinâmicos. Eles mudam de estado ao longo do tempo e realizam funções. O SysML fornece vários diagramas para modelar o comportamento, incluindo Diagramas de Máquina de Estados, Diagramas de Atividade e Diagramas de Sequência. A validação comportamental garante que a lógica flua corretamente.

Máquinas de estado são cruciais para sistemas com ciclos de vida ou modos operacionais complexos.

Diagramas de atividade modelam o fluxo de controle ou dados através de um processo.

Uma das partes mais críticas do SysML é a capacidade de vincular requisitos a elementos de design. Sem essa rastreabilidade, o modelo perde seu propósito como um artefato de engenharia de sistemas. A validação aqui garante que cada requisito seja abordado e cada elemento de design seja justificado.

Diagramas paramétricos permitem que engenheiros definam restrições matemáticas sobre parâmetros do sistema. Isso é vital para análise de desempenho e viabilidade física.

Uma lista de verificação é uma ferramenta, mas o processo é humano. As revisões de arquitetura devem ser eventos colaborativos que envolvam arquitetos de sistemas, engenheiros e partes interessadas. O objetivo não é encontrar falhas, mas identificar lacunas.

Para referência rápida, a tabela a seguir resume os pontos críticos de validação em todos os tipos principais de diagramas SysML. Essa tabela pode ser usada como uma lista de verificação física ou digital durante as sessões de revisão.

| Categoria | Item de Verificação | Prioridade | Método de Verificação |

|---|---|---|---|

| Estrutura (BDD) | Todos os blocos têm nomes únicos | Alta | Pesquisar duplicatas |

| Estrutura (BDD) | Os atributos têm tipos de dados válidos | Médio | Inspeção de tipo |

| Estrutura (IBD) | Todas as portas têm interfaces tipadas | Alto | Validação de interface |

| Estrutura (IBD) | Conectores correspondem aos tipos de portas | Alto | Validação de fluxo |

| Comportamento | Máquinas de estado têm estados iniciais | Alto | Inspeção de diagrama |

| Comportamento | Todas as transições têm condições de guarda | Médio | Verificação lógica |

| Requisitos | 100% dos requisitos têm links de satisfação | Alto | Matriz de rastreabilidade |

| Requisitos | Nenhum requisito órfão | Alto | Análise de links |

| Restrições | As equações são dimensionalmente consistentes | Médio | Análise de unidades |

| Restrições | Variáveis são definidas antes do uso | Alto | Gráfico de dependência |

| Geral | O modelo está em conformidade com perfis padrão | Médio | Validação de perfil |

| Geral | Sem links quebrados ou erros | Crítico | Compilador de modelo |

Mesmo com uma lista de verificação, as equipes frequentemente caem em armadilhas. Compreender esses problemas comuns pode ajudar a evitá-los.

Criar um modelo muito detalhado muito cedo pode obscurecer a arquitetura.Solução: Foque primeiro no nível do sistema. Descer em detalhes apenas quando necessário para subsistemas específicos.

Modelos mudam frequentemente. Se uma exigência mudar, mas o modelo não, a rastreabilidade é quebrada.Solução: Integre processos de gestão de mudanças com o fluxo de trabalho de modelagem.

Usar notações diferentes para conceitos semelhantes confunde os leitores.Solução: Estabeleça um padrão de modelagem ou guia de estilo no início do projeto.

Engenheiros constroem o modelo, mas os stakeholders devem validá-lo.Solução: Agende sessões regulares de revisão onde stakeholders não técnicos possam visualizar o modelo.

A validação não é um evento único. É uma atividade contínua ao longo de todo o ciclo de vida do sistema. À medida que os requisitos evoluem, o modelo deve evoluir junto com eles.

Ao tratar o modelo SysML como um artefato vivo, a equipe de engenharia garante que o gêmeo digital permaneça uma representação precisa do sistema físico. Esse alinhamento é o valor central da modelagem de sistemas.

O rigor aplicado à validação do modelo está diretamente correlacionado à qualidade do sistema final. Um modelo bem validado reduz a ambiguidade, melhora a comunicação e minimiza o risco de falhas no sistema. As listas de verificação e os processos descritos aqui fornecem uma estrutura para manter essa integridade.

Lembre-se de que as ferramentas auxiliam o processo, mas o julgamento humano é irreplaceável. Verificações automatizadas detectam erros de sintaxe, mas apenas engenheiros conseguem detectar erros semânticos. Combinar validação técnica com revisão de especialistas cria uma defesa robusta contra defeitos no sistema.

Implementar essas práticas exige disciplina, mas o retorno sobre o investimento é substancial. Sistemas construídos com modelos validados são mais confiáveis, mais fáceis de manter e mais seguros para operar. O esforço gasto na revisão é um investimento na longevidade e no sucesso do projeto de engenharia.