Visual Paradigm Desktop |

Visual Paradigm Desktop |  Visual Paradigm Online

Visual Paradigm OnlineLa ingeniería de sistemas depende en gran medida de la precisión de sus modelos. Cuando se utiliza el Lenguaje de Modelado de Sistemas (SysML), la complejidad de las interacciones del sistema, los requisitos y las restricciones puede aumentar rápidamente si no se gestiona rigurosamente. Un modelo no es meramente un dibujo; es una representación digital de la realidad que impulsa el desarrollo, las pruebas y la verificación. Por lo tanto, listas de verificación de validación de modelos para revisiones de arquitectura de SysMLson herramientas esenciales para garantizar la integridad.

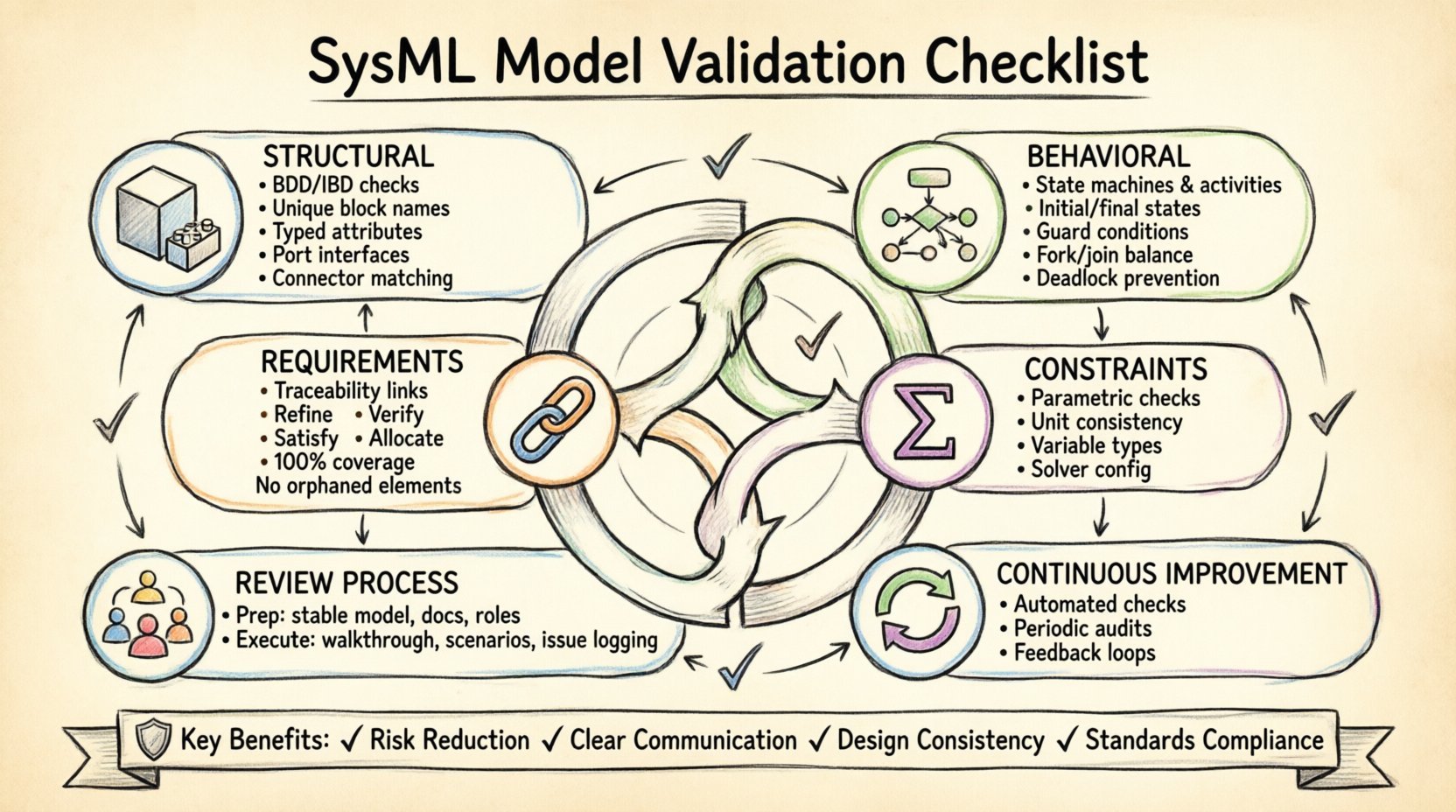

Esta guía ofrece una revisión detallada de los pasos necesarios para validar un modelo de SysML. Cubre la consistencia estructural, la lógica comportamental, la trazabilidad de requisitos y la satisfacción de restricciones. Al adherirse a estas normas, los equipos de ingeniería pueden reducir riesgos y mejorar la fidelidad de sus diseños arquitectónicos.

La validación en la ingeniería de sistemas es el proceso de confirmar que el modelo representa correctamente el sistema deseado. Difiere de la verificación, que pregunta si el sistema cumple con los requisitos especificados. La validación pregunta si se está construyendo el sistema correcto. En el contexto de SysML, esto implica comprobar la sintaxis del lenguaje y la semántica de los elementos del modelo.

Al realizar una revisión de arquitectura, el objetivo es identificar discrepancias antes de que comience la generación de código o la prototipación física. Los errores detectados en esta etapa son significativamente más baratos de corregir que los encontrados durante la fabricación o la implementación. Un enfoque estructurado garantiza que no se omita ningún elemento crítico.

La base de cualquier modelo de SysML reside en su estructura. Esto se representa principalmente en los Diagramas de Definición de Bloques (BDD) y los Diagramas Internos de Bloques (IBD). La validación estructural garantiza que la composición física y lógica del sistema sea sólida.

Los bloques representan los componentes físicos o lógicos del sistema. Al revisar los BDD, enfóquese en lo siguiente:

Los IBDs describen cómo interactúan los bloques internamente. Aquí se define el flujo de materia, energía y datos.

Los sistemas son dinámicos. Cambian de estado con el tiempo y realizan funciones. SysML proporciona varios diagramas para modelar el comportamiento, incluyendo diagramas de máquinas de estados, diagramas de actividades y diagramas de secuencia. La validación comportamental asegura que la lógica fluya correctamente.

Las máquinas de estados son cruciales para sistemas con ciclos de vida o modos operativos complejos.

Los diagramas de actividades modelan el flujo de control o datos a través de un proceso.

Uno de los aspectos más críticos de SysML es la capacidad de vincular requisitos con elementos de diseño. Sin esta rastreabilidad, el modelo pierde su propósito como un artefacto de ingeniería de sistemas. La validación aquí asegura que cada requisito sea abordado y que cada elemento de diseño esté justificado.

Los diagramas paramétricos permiten a los ingenieros definir restricciones matemáticas sobre los parámetros del sistema. Esto es fundamental para el análisis de rendimiento y la viabilidad física.

Una lista de verificación es una herramienta, pero el proceso es humano. Las revisiones de arquitectura deben ser eventos colaborativos que involucren arquitectos de sistemas, ingenieros y partes interesadas. El objetivo no es encontrar fallos, sino identificar brechas.

Para referencia rápida, la siguiente tabla resume los puntos críticos de validación en los principales tipos de diagramas SysML. Esta tabla puede usarse como una lista de verificación física o digital durante las sesiones de revisión.

| Categoría | Elemento de verificación | Prioridad | Método de verificación |

|---|---|---|---|

| Estructura (BDD) | Todos los bloques tienen nombres únicos | Alta | Buscar duplicados |

| Estructura (BDD) | Los atributos tienen tipos de datos válidos | Medio | Inspección de tipo |

| Estructura (IBD) | Todos los puertos tienen interfaces tipificadas | Alto | Validación de interfaz |

| Estructura (IBD) | Los conectores coinciden con los tipos de puertos | Alto | Validación de flujo |

| Comportamiento | Las máquinas de estado tienen estados iniciales | Alto | Inspección de diagrama |

| Comportamiento | Todas las transiciones tienen condiciones de guarda | Medio | Verificación lógica |

| Requisitos | El 100 % de los requisitos tienen enlaces de satisfacción | Alto | Matriz de trazabilidad |

| Requisitos | No hay requisitos huérfanos | Alto | Análisis de enlaces |

| Restricciones | Las ecuaciones son dimensionalmente coherentes | Medio | Análisis de unidades |

| Restricciones | Las variables se definen antes de usarlas | Alto | Gráfico de dependencias |

| General | El modelo cumple con los perfiles estándar | Medio | Validación de perfil |

| General | Sin enlaces rotos ni errores | Crítico | Compilador de modelo |

Aunque se cuente con una lista de verificación, los equipos a menudo caen en trampas. Comprender estos problemas comunes puede ayudar a prevenirlos.

Crear un modelo demasiado detallado demasiado pronto puede ocultar la arquitectura.Solución:Enfóquese primero en el nivel del sistema. Descienda solo cuando sea necesario para subsistemas específicos.

Los modelos cambian con frecuencia. Si un requisito cambia pero el modelo no, se pierde la trazabilidad.Solución:Integre los procesos de gestión de cambios con el flujo de trabajo de modelado.

Usar notaciones diferentes para conceptos similares confunde a los lectores.Solución:Establezca una norma de modelado o una guía de estilo al inicio del proyecto.

Los ingenieros construyen el modelo, pero los interesados deben validarlo.Solución:Programar sesiones regulares de revisión donde los interesados no técnicos puedan ver el modelo.

La validación no es un evento único. Es una actividad continua durante todo el ciclo de vida del sistema. A medida que evolucionan los requisitos, el modelo debe evolucionar con ellos.

Al tratar el modelo SysML como un artefacto vivo, el equipo de ingeniería garantiza que el gemelo digital permanezca una representación precisa del sistema físico. Esta alineación es el valor fundamental de la modelización de sistemas.

El rigor aplicado a la validación del modelo se correlaciona directamente con la calidad del sistema final. Un modelo bien validado reduce la ambigüedad, mejora la comunicación y minimiza el riesgo de fallos del sistema. Las listas de verificación y los procesos descritos aquí proporcionan un marco para mantener esa integridad.

Recuerde que las herramientas ayudan al proceso, pero el juicio humano es irremplazable. Las verificaciones automatizadas detectan errores de sintaxis, pero solo los ingenieros pueden detectar errores semánticos. Combinar la validación técnica con la revisión de expertos crea una defensa sólida contra los defectos del sistema.

Implementar estas prácticas requiere disciplina, pero el retorno de la inversión es sustancial. Los sistemas construidos sobre modelos validados son más confiables, más fáciles de mantener y más seguros de operar. El esfuerzo invertido en la revisión es una inversión en la longevidad y el éxito del proyecto de ingeniería.