Visual Paradigm Desktop |

Visual Paradigm Desktop |  Visual Paradigm Online

Visual Paradigm OnlineEngenharia de sistemas que impulsionam a aviação, saúde, defesa e infraestrutura exige um nível de precisão que os métodos tradicionais de documentação frequentemente têm dificuldade em manter. À medida que a complexidade cresce, o risco de ambiguidade aumenta. É aqui que a Linguagem de Modelagem de Sistemas (SysML) se torna indispensável. No entanto, criar um modelo é apenas o começo. O verdadeiro valor reside em verificar se o modelo representa com precisão o comportamento pretendido do sistema e atende a todos os requisitos críticos. Este guia apresenta uma abordagem abrangente para estabelecer uma estratégia de verificação dentro de um framework de Engenharia de Sistemas Baseada em Modelos (MBSE).

A verificação responde à pergunta: Estamos construindo o produto corretamente? No contexto do SysML, isso significa garantir que o próprio modelo seja correto, consistente e completo em relação aos requisitos e especificações de design definidos. É distinto da validação, que pergunta se estamos construindo o produto certo. A verificação foca na lógica interna, sintaxe e correção semântica dos diagramas e requisitos.

Sem uma estratégia de verificação rigorosa, os modelos podem se afastar de seu propósito original. Um diagrama de definição de blocos pode mostrar uma conexão fisicamente impossível. Um diagrama de atividades pode descrever uma sequência que leva a um deadlock. Esses erros são custosos se forem descobertos tardiamente no ciclo de vida do desenvolvimento. Portanto, a verificação deve ser integrada cedo e com frequência.

Sistemas críticos para a missão diferem dos produtos comerciais em sua tolerância a falhas. Nestes setores, uma falha pode resultar na perda de vidas, danos financeiros significativos ou riscos à segurança nacional. Consequentemente, a estratégia de verificação deve ser mais rigorosa do que os protocolos padrão de testes de software.

Os seguintes fatores definem o ambiente de alto risco:

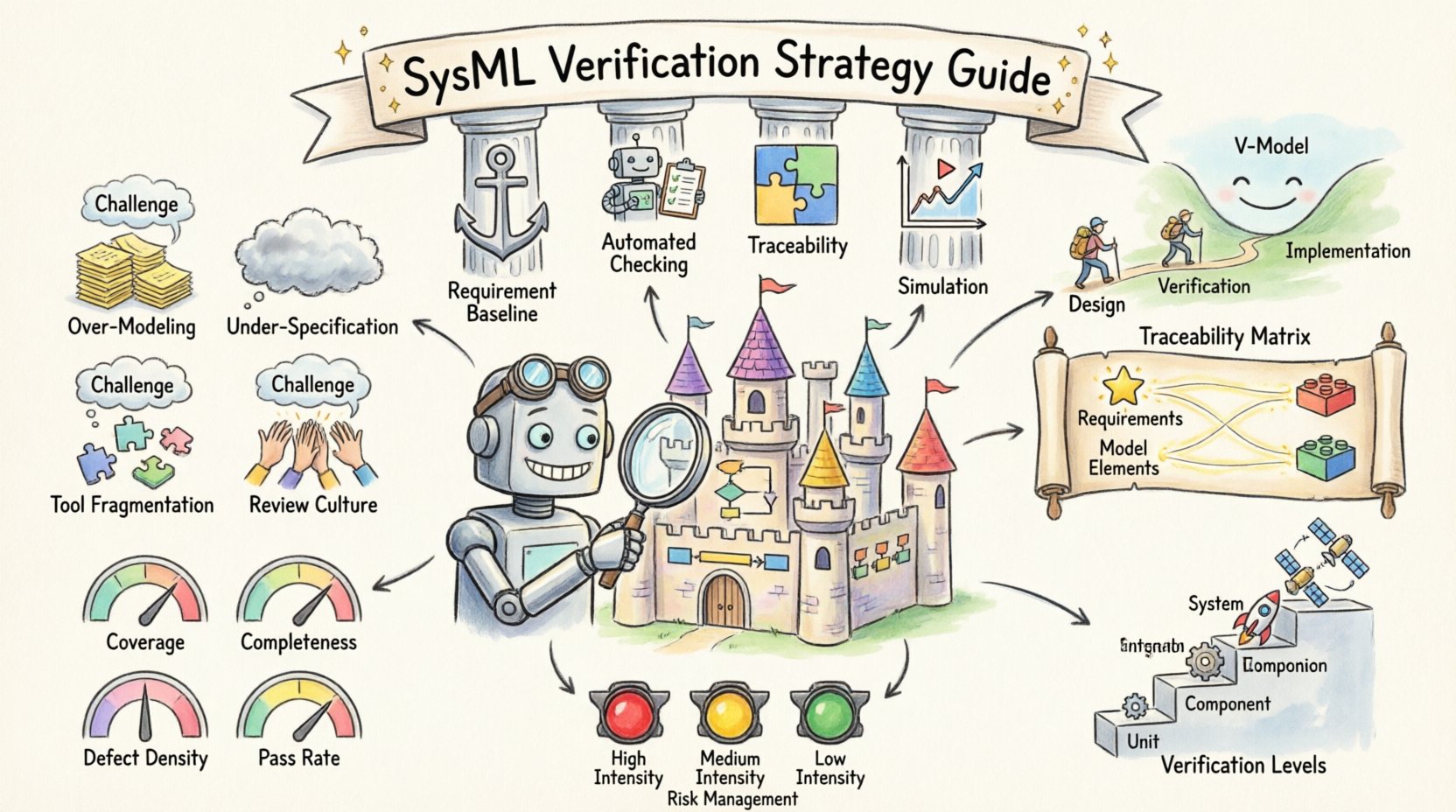

Uma estratégia bem-sucedida repousa sobre quatro pilares fundamentais. Ignorar qualquer um desses pode comprometer a integridade de toda a entrega.

A verificação não pode começar se os requisitos forem fluidos. Embora as mudanças sejam inevitáveis, o processo de verificação exige uma base estável. Você deve definir procedimentos de controle de mudanças que garantam que qualquer modificação a um requisito desencadeie uma revisão dos elementos de modelo associados.

A revisão manual é propensa a erros humanos. Devem ser utilizadas ferramentas automatizadas para verificar erros comuns na modelagem. Isso inclui a verificação de blocos órfãos, portas não conectadas e dependências circulares. A automação permite que engenheiros se concentrem na lógica em vez da sintaxe.

A rastreabilidade liga requisitos a elementos de design. No SysML, isso geralmente é alcançado por meio de Diagramas de Requisitos e relacionamentos de rastreabilidade. Uma estratégia sólida garante que cada requisito tenha um status de verificação (Aprovado, Reprovado ou Não Verificado).

Modelos SysML são representações estáticas. Para verificar o comportamento dinâmico, a simulação é frequentemente necessária. Diagramas paramétricos podem ser usados para verificar restrições físicas, enquanto diagramas de atividade podem ser analisados quanto ao fluxo lógico. A simulação fecha a lacuna entre o design abstrato e o comportamento concreto.

O plano de verificação é o documento que regula todo o processo. Ele define o escopo, os recursos, o cronograma e os métodos de verificação. Ele não deve ser um documento estático, mas uma artefato vivo que evolui com o projeto.

| Elemento | Descrição | Nível de Importância |

|---|---|---|

| Escopo | Define quais modelos e requisitos estão incluídos. | Crítico |

| Ferramentas | Especifica os ambientes de modelagem e análise utilizados. | Alto |

| Funções | Identifica quem realiza a verificação (engenheiros, revisores, auditores). | Alto |

| Métricas | Define como o sucesso é medido (cobertura, taxa de defeitos). | Médio |

| Critérios de Entrada/Saída | Condições necessárias para iniciar e encerrar as atividades de verificação. | Crítico |

A execução envolve a realização das verificações definidas no plano. O objetivo é gerar evidências de que o modelo atende aos requisitos. Essas evidências são cruciais para certificação e auditoria.

A Matriz de Rastreabilidade é o artefato central para rastrear o status de verificação. Ela vincula cada requisito ao elemento específico do modelo que o satisfaz. Em um ambiente SysML, isso geralmente é uma relação direta dentro do próprio modelo.

Níveis diferentes de verificação se aplicam a partes diferentes do modelo. A tabela abaixo descreve a hierarquia típica.

| Nível | Foco | Atividade Típica |

|---|---|---|

| Verificação de Unidade | Blocos/Attributos Individuais | Consistência de atributos, restrições de parâmetros |

| Verificação de Componente | Subsistemas | Compatibilidade de interface, fluxo lógico interno |

| Verificação de Sistema | Arquitetura Completa | Requisitos de ponta a ponta, simulação de cenários |

| Verificação de Integração | Interfaces Externas | Hardware em laço, estresse ambiental |

Como você sabe que a estratégia está funcionando? Você precisa de métricas quantitativas. Essas métricas fornecem visibilidade sobre a saúde do projeto e a qualidade dos modelos.

Mesmo com um plano bem definido, as organizações enfrentam obstáculos. Reconhecer esses perigos cedo permite uma mitigação proativa.

Criar modelos detalhados para áreas que não são críticas para a função principal do sistema desperdiça tempo e recursos. Foque os esforços de verificação em áreas de alto risco e alta complexidade.

Requisitos vagos tornam a verificação impossível. Se um requisito diz “O sistema deve responder rapidamente”, não há métrica para verificar. Os requisitos devem ser mensuráveis e inequívocos.

Usar ferramentas diferentes para requisitos, modelagem e testes pode quebrar a rastreabilidade. Certifique-se de que o ecossistema suporte a troca de dados e mantenha os links ao longo de todo o ciclo de vida.

A automação é poderosa, mas não pode substituir o julgamento humano. Revisões por pares do modelo são essenciais para detectar erros lógicos que os scripts podem ignorar.

A verificação não deve ser uma fase separada no final do projeto. Ela deve ser integrada ao ciclo de vida do desenvolvimento. O Modelo em V é um framework comum para essa integração.

| Lado Esquerdo (Projeto) | Centro (Verificação) | Lado Direito (Implementação) |

|---|---|---|

| Requisitos do Sistema | Verificação do Sistema | Integração de Sistema |

| Arquitetura de Sistema | Verificação de Arquitetura | Integração de Sistema |

| Projeto de Componente | Verificação de Componente | Teste de Componente |

| Projeto de Módulo | Verificação de Módulo | Teste de Unidade |

Ao alinhar as atividades de verificação do SysML com esta estrutura, as equipes garantem que as decisões de projeto sejam validadas antes da produção de código ou hardware. Isso reduz significativamente os custos com retrabalho.

Além das verificações básicas, técnicas avançadas podem fornecer insights mais profundos sobre o comportamento do sistema.

Esses diagramas permitem que engenheiros modelam restrições físicas e relações matemáticas. São essenciais para verificar requisitos de desempenho, como consumo de energia, limites térmicos ou tolerâncias a estresse. Resolver as equações dentro desses diagramas fornece prova de que o projeto atende às leis da física.

Para sistemas com lógica complexa, os Diagramas de Máquina de Estados são vitais. A verificação aqui envolve verificar deadlocks, estados inacessíveis e lógica de transição correta. Isso garante que o sistema se comporte corretamente sob todas as condições possíveis.

Defina casos de uso que representem o uso do mundo real. Modele esses cenários no ambiente SysML para verificar se o sistema os trata conforme esperado. Isso ajuda a identificar casos de borda que podem não aparecer nos testes funcionais padrão.

O esforço de verificação deve ser proporcional ao risco. Nem todos os requisitos têm o mesmo peso. Um requisito crítico para a segurança exige um nível mais alto de verificação do que um requisito meramente estético.

Ao mapear riscos ao esforço de verificação, as equipes podem otimizar recursos mantendo os padrões de segurança.

Sistemas críticos para missões muitas vezes sobrevivem às equipes que os construíram. Os artefatos de verificação devem ser mantidos. Isso significa:

Adotar uma estratégia de verificação em SysML é uma mudança cultural. Ela move a organização de uma engenharia centrada em documentos para uma engenharia centrada em modelos. Essa transição exige disciplina, treinamento e compromisso com a qualidade. No entanto, os benefícios são substanciais: redução de riscos, custos menores e maior confiança no produto final.

O sucesso depende da aplicação consistente da estratégia. Não é uma atividade pontual, mas um processo contínuo que ocorre paralelamente ao desenvolvimento. Ao incorporar a verificação em cada etapa do fluxo de trabalho, as organizações podem entregar sistemas críticos com a confiabilidade que exigem.

Lembre-se de que o modelo é uma ferramenta de comunicação tanto quanto é uma especificação. Um modelo verificado é uma compreensão verificada do sistema. Esse entendimento compartilhado é a base para a entrega bem-sucedida de sistemas.