Visual Paradigm Desktop |

Visual Paradigm Desktop |  Visual Paradigm Online

Visual Paradigm OnlineEl diseño de sistemas que impulsan la aviación, la salud, la defensa y la infraestructura requiere un nivel de precisión que los métodos tradicionales de documentación a menudo tienen dificultades para mantener. A medida que crece la complejidad, aumenta el riesgo de ambigüedad. Es aquí donde el Lenguaje de Modelado de Sistemas (SysML) se vuelve indispensable. Sin embargo, crear un modelo es solo el primer paso. El verdadero valor reside en verificar que el modelo represente con precisión el comportamiento del sistema deseado y cumpla con todos los requisitos críticos. Esta guía describe un enfoque integral para establecer una estrategia de verificación dentro de un marco de Ingeniería de Sistemas Basada en Modelos (MBSE).

La verificación responde a la pregunta:¿Estamos construyendo el producto correctamente? En el contexto de SysML, esto significa garantizar que el modelo en sí sea correcto, consistente y completo en relación con los requisitos y especificaciones de diseño definidos. Es distinto de la validación, que pregunta si estamos construyendo el producto correcto. La verificación se centra en la lógica interna, la sintaxis y la corrección semántica de los diagramas y los requisitos.

Sin una estrategia de verificación rigurosa, los modelos pueden desviarse de su intención original. Un diagrama de definición de bloques podría mostrar una conexión que es físicamente imposible. Un diagrama de actividades podría describir una secuencia que conduce a un bloqueo. Estos errores son costosos si se descubren tarde en el ciclo de desarrollo. Por lo tanto, la verificación debe integrarse desde temprano y con frecuencia.

Los sistemas críticos para la misión difieren de los productos comerciales en su tolerancia al fallo. En estos sectores, un fallo puede provocar pérdida de vidas, daños financieros significativos o riesgos para la seguridad nacional. En consecuencia, la estrategia de verificación debe ser más rigurosa que los protocolos estándar de pruebas de software.

Los siguientes factores definen el entorno de alto riesgo:

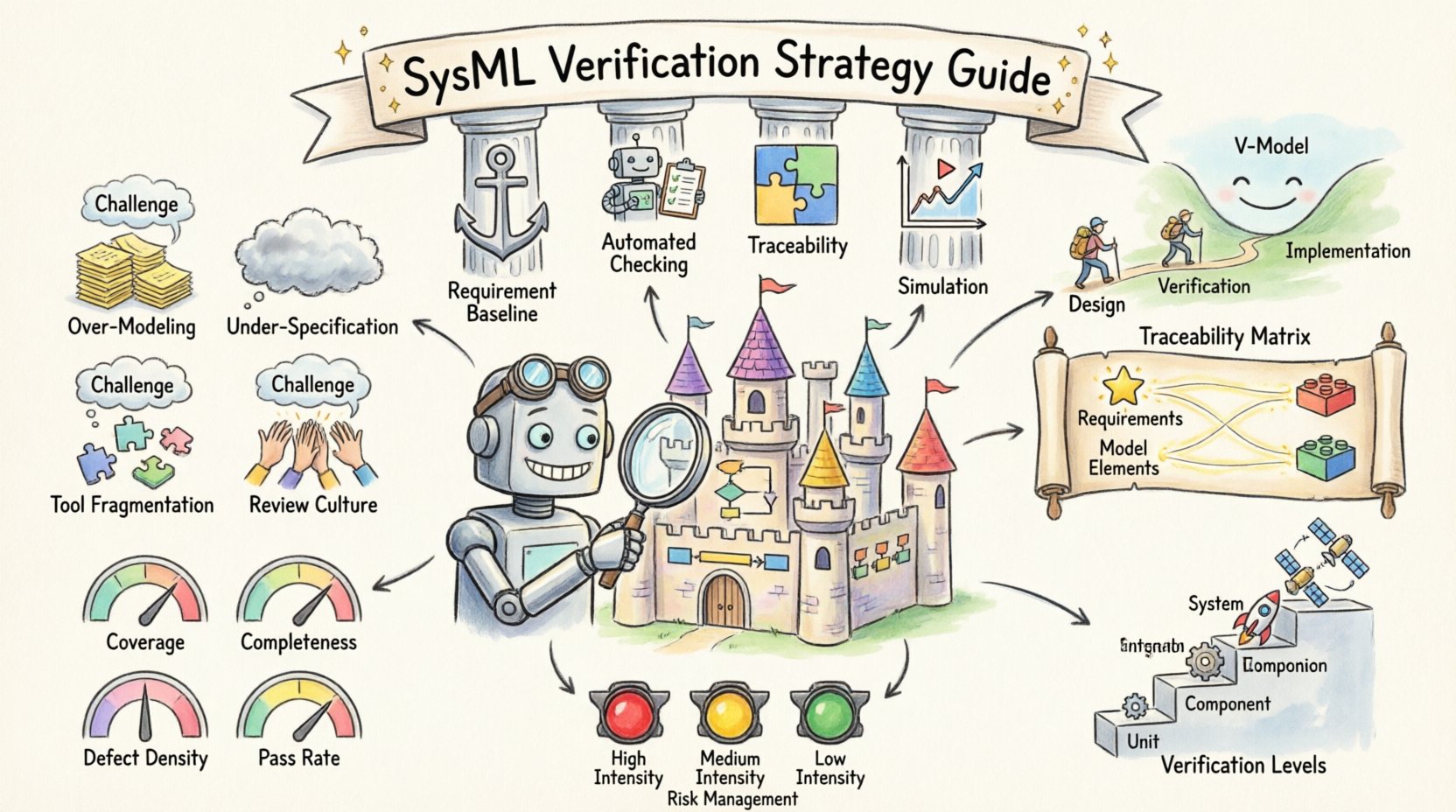

Una estrategia exitosa se basa en cuatro pilares fundamentales. Descuidar cualquiera de ellos puede comprometer la integridad de toda la entrega.

La verificación no puede comenzar si los requisitos son cambiantes. Aunque los cambios son inevitables, el proceso de verificación requiere una base estable. Debe definir procedimientos de control de cambios que garanticen que cualquier modificación a un requisito desencadene una revisión de los elementos de modelo asociados.

La revisión manual está sujeta a errores humanos. Deben emplearse herramientas automatizadas para verificar errores comunes en la modelización. Esto incluye comprobar bloques huérfanos, puertos sin conectar y dependencias circulares. La automatización permite a los ingenieros centrarse en la lógica en lugar de la sintaxis.

La trazabilidad vincula los requisitos a los elementos de diseño. En SysML, esto se logra a menudo mediante Diagramas de Requisitos y relaciones de trazabilidad. Una estrategia sólida garantiza que cada requisito tenga un estado de verificación (Aprobado, Fallido o No verificado).

Los modelos de SysML son representaciones estáticas. Para verificar el comportamiento dinámico, a menudo se requiere simulación. Los diagramas paramétricos pueden usarse para verificar restricciones físicas, mientras que los diagramas de actividad pueden analizarse para evaluar el flujo lógico. La simulación cierra la brecha entre el diseño abstracto y el comportamiento concreto.

El plan de verificación es el documento que rige todo el proceso. Define el alcance, los recursos, el cronograma y los métodos de verificación. No debe ser un documento estático, sino un artefacto vivo que evolucione con el proyecto.

| Elemento | Descripción | Nivel de importancia |

|---|---|---|

| Alcance | Define qué modelos y requisitos están incluidos. | Crítico |

| Herramientas | Especifica los entornos de modelado y análisis utilizados. | Alto |

| Roles | Identifica quién realiza la verificación (ingenieros, revisores, auditores). | Alto |

| Métricas | Define cómo se mide el éxito (cobertura, tasa de defectos). | Medio |

| Criterios de entrada/salida | Condiciones necesarias para iniciar y finalizar las actividades de verificación. | Crítico |

La ejecución implica realizar las comprobaciones definidas en el plan. El objetivo es generar evidencia de que el modelo cumple con los requisitos. Esta evidencia es crucial para la certificación y la auditoría.

La Matriz de Rastreabilidad es el artefacto central para rastrear el estado de verificación. Enlaza cada requisito con el elemento específico del modelo que lo satisface. En un entorno SysML, esta relación suele ser directa dentro del propio modelo.

Diferentes niveles de verificación se aplican a distintas partes del modelo. La tabla a continuación describe la jerarquía típica.

| Nivel | Enfoque | Actividad típica |

|---|---|---|

| Verificación de unidad | Bloques/atributos individuales | Consistencia de atributos, restricciones de parámetros |

| Verificación de componente | Subsistemas | Compatibilidad de interfaz, flujo lógico interno |

| Verificación del sistema | Arquitectura completa | Requisitos de extremo a extremo, simulación de escenarios |

| Verificación de integración | Interfaces externas | Hardware en el bucle, estrés ambiental |

¿Cómo sabes que la estrategia está funcionando? Necesitas métricas cuantitativas. Estas métricas proporcionan visibilidad sobre el estado del proyecto y la calidad de los modelos.

Aunque se cuente con un plan bien definido, las organizaciones enfrentan obstáculos. Reconocer estos problemas temprano permite una mitigación proactiva.

Crear modelos detallados para áreas que no son críticas para la función principal del sistema desperdicia tiempo y recursos. Enfóquese en el esfuerzo de verificación en áreas de alto riesgo y alta complejidad.

Los requisitos ambiguos hacen imposible la verificación. Si un requisito dice «El sistema deberá responder rápidamente», no existe ninguna métrica para verificarlo. Los requisitos deben ser medibles y no ambiguos.

Usar herramientas diferentes para requisitos, modelado y pruebas puede romper la trazabilidad. Asegúrese de que el ecosistema permita el intercambio de datos y mantenga los enlaces a lo largo de todo el ciclo de vida.

La automatización es poderosa, pero no puede reemplazar el juicio humano. Las revisiones entre pares del modelo son esenciales para detectar errores lógicos que los scripts podrían pasar por alto.

La verificación no debe ser una fase separada al final del proyecto. Debe integrarse en el ciclo de vida del desarrollo. El modelo en V es un marco común para esta integración.

| Lado izquierdo (Diseño) | Centro (Verificación) | Lado derecho (Implementación) |

|---|---|---|

| Requisitos del sistema | Verificación del sistema | Integración de sistemas |

| Arquitectura de sistemas | Verificación de arquitectura | Integración de sistemas |

| Diseño de componentes | Verificación de componentes | Pruebas de componentes |

| Diseño de módulos | Verificación de módulos | Pruebas unitarias |

Al alinear las actividades de verificación de SysML con esta estructura, los equipos aseguran que las decisiones de diseño se validen antes de producir código o hardware. Esto reduce significativamente los costos de rehacer trabajos.

Más allá de las verificaciones básicas, las técnicas avanzadas pueden proporcionar una comprensión más profunda del comportamiento del sistema.

Estos diagramas permiten a los ingenieros modelar restricciones físicas y relaciones matemáticas. Son esenciales para verificar requisitos de rendimiento como el consumo de energía, los límites térmicos o las tolerancias a esfuerzos. Resolver las ecuaciones dentro de estos diagramas proporciona prueba de que el diseño cumple con las leyes físicas.

Para sistemas con lógica compleja, los diagramas de máquinas de estado son vitales. La verificación aquí implica comprobar la existencia de bloqueos, estados inalcanzables y lógica de transición adecuada. Asegura que el sistema se comporte correctamente bajo todas las condiciones posibles.

Defina casos de uso que representen el uso del mundo real. Modele estos escenarios en el entorno de SysML para ver si el sistema los maneja como se espera. Esto ayuda a descubrir casos límite que podrían no aparecer en las pruebas funcionales estándar.

El esfuerzo de verificación debe ser proporcional al riesgo. No todos los requisitos tienen el mismo peso. Un requisito crítico para la seguridad requiere un nivel más alto de verificación que uno puramente estético.

Al asignar riesgos al esfuerzo de verificación, los equipos pueden optimizar los recursos manteniendo los estándares de seguridad.

Los sistemas críticos para la misión a menudo sobreviven a los equipos que los construyeron. Los artefactos de verificación deben ser mantenibles. Esto significa:

Adoptar una estrategia de verificación de SysML es un cambio cultural. Transforma a la organización de una ingeniería centrada en documentos a una centrada en modelos. Esta transición requiere disciplina, capacitación y un compromiso con la calidad. Sin embargo, los beneficios son sustanciales: reducción de riesgos, costos más bajos y mayor confianza en el producto final.

El éxito depende de la aplicación consistente de la estrategia. No es una actividad puntual, sino un proceso continuo que opera paralelamente al desarrollo. Al integrar la verificación en cada paso del flujo de trabajo, las organizaciones pueden entregar sistemas críticos para la misión con la confiabilidad que exigen.

Recuerde que el modelo es una herramienta de comunicación tanto como una especificación. Un modelo verificado es una comprensión verificada del sistema. Esta comprensión compartida es la base para la entrega exitosa del sistema.