Visual Paradigm Desktop |

Visual Paradigm Desktop |  Visual Paradigm Online

Visual Paradigm OnlineMengembangkan sistem yang mendorong penerbangan, kesehatan, pertahanan, dan infrastruktur membutuhkan tingkat presisi yang sering kali sulit dipertahankan oleh metode dokumentasi tradisional. Seiring kompleksitas meningkat, risiko ambiguitas juga meningkat. Di sinilah Bahasa Pemodelan Sistem (SysML) menjadi sangat penting. Namun, membuat model hanyalah awal dari proses. Nilai sejati terletak pada verifikasi bahwa model tersebut secara akurat merepresentasikan perilaku sistem yang dimaksudkan dan memenuhi semua persyaratan kritis. Panduan ini menguraikan pendekatan komprehensif untuk membangun strategi verifikasi dalam kerangka Kerangka Kerja Insinyur Sistem Berbasis Model (MBSE).

Verifikasi menjawab pertanyaan: Apakah kita sedang membangun produk dengan benar?Dalam konteks SysML, ini berarti memastikan bahwa model itu sendiri benar, konsisten, dan lengkap terhadap persyaratan dan spesifikasi desain yang telah ditetapkan. Ini berbeda dari validasi, yang menanyakan apakah kita sedang membangun produk yang tepat. Verifikasi berfokus pada logika internal, tata bahasa, dan kebenaran semantik dari diagram dan persyaratan.

Tanpa strategi verifikasi yang ketat, model bisa menyimpang dari tujuan awalnya. Diagram definisi blok mungkin menunjukkan koneksi yang secara fisik mustahil. Diagram aktivitas mungkin menggambarkan urutan yang mengarah pada deadlock. Kesalahan-kesalahan ini mahal jika ditemukan terlambat dalam siklus pengembangan. Oleh karena itu, verifikasi harus diintegrasikan sejak awal dan secara rutin.

Sistem kritis misi berbeda dari produk komersial dalam toleransi terhadap kegagalan. Di sektor-sektor ini, kegagalan dapat menyebabkan kehilangan nyawa, kerusakan finansial besar, atau risiko keamanan nasional. Akibatnya, strategi verifikasi harus lebih ketat daripada protokol pengujian perangkat lunak standar.

Faktor-faktor berikut mendefinisikan lingkungan berisiko tinggi:

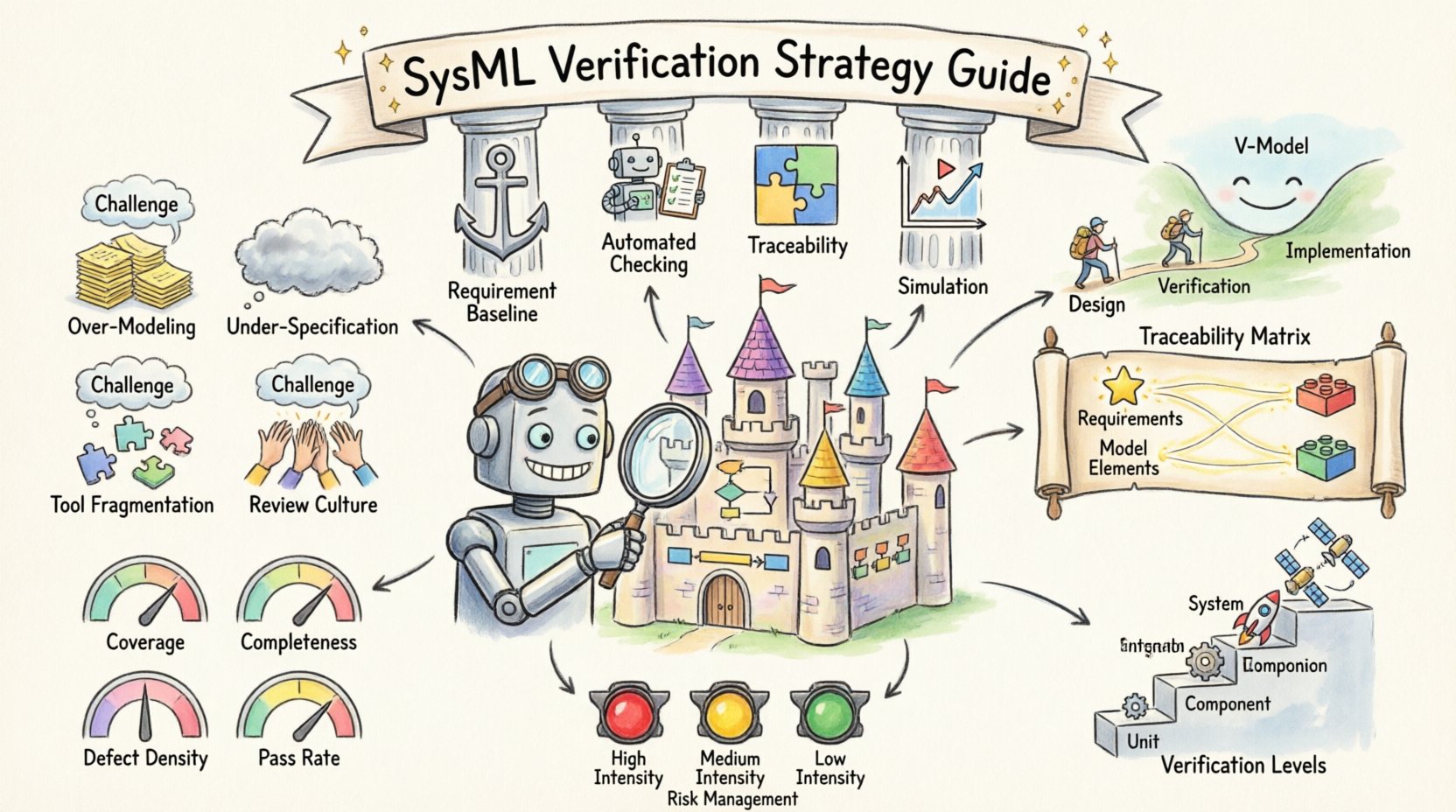

Strategi yang sukses berdiri di atas empat pilar dasar. Mengabaikan salah satu dari pilar ini dapat membahayakan integritas seluruh pengiriman.

Verifikasi tidak dapat dimulai jika persyaratan bersifat berubah-ubah. Meskipun perubahan adalah hal yang tak terhindarkan, proses verifikasi membutuhkan dasar yang stabil. Anda harus menentukan prosedur kontrol perubahan yang memastikan setiap modifikasi terhadap persyaratan memicu tinjauan terhadap elemen model yang terkait.

Tinjauan manual rentan terhadap kesalahan manusia. Alat otomatis harus digunakan untuk memeriksa kesalahan pemodelan umum. Ini mencakup pemeriksaan terhadap blok yang terpisah, port yang tidak terhubung, dan ketergantungan melingkar. Otomasi memungkinkan insinyur fokus pada logika daripada sintaks.

Lacak menghubungkan persyaratan dengan elemen desain. Dalam SysML, hal ini sering dicapai melalui Diagram Persyaratan dan hubungan lacak. Strategi yang kuat memastikan setiap persyaratan memiliki status verifikasi (Lolos, Gagal, atau Belum Diverifikasi).

Model SysML adalah representasi statis. Untuk memverifikasi perilaku dinamis, simulasi sering diperlukan. Diagram parametrik dapat digunakan untuk memverifikasi batasan fisik, sementara diagram aktivitas dapat dianalisis untuk alur logika. Simulasi menghubungkan kesenjangan antara desain abstrak dan perilaku nyata.

Rencana verifikasi adalah dokumen yang mengatur seluruh proses. Dokumen ini menentukan cakupan, sumber daya, jadwal, dan metode verifikasi. Dokumen ini seharusnya tidak statis, melainkan merupakan artefak hidup yang berkembang seiring proyek.

| Elemen | Deskripsi | Tingkat Kepentingan |

|---|---|---|

| Cakupan | Menentukan model dan persyaratan mana yang termasuk. | Kritis |

| Alat | Menentukan lingkungan pemodelan dan analisis yang digunakan. | Tinggi |

| Peran | Mengidentifikasi siapa yang melakukan verifikasi (insinyur, peninjau, auditor). | Tinggi |

| Metrik | Menentukan bagaimana keberhasilan diukur (cakupan, tingkat cacat). | Sedang |

| Kriteria Masuk/Keluar | Kondisi yang diperlukan untuk memulai dan mengakhiri kegiatan verifikasi. | Kritis |

Eksekusi melibatkan menjalankan pemeriksaan yang ditentukan dalam rencana. Tujuannya adalah menghasilkan bukti bahwa model memenuhi persyaratan. Bukti ini sangat penting untuk sertifikasi dan audit.

Matriks Pelacakan adalah artefak utama untuk melacak status verifikasi. Ini menghubungkan setiap kebutuhan dengan elemen model tertentu yang memenuhinya. Dalam lingkungan SysML, ini sering merupakan hubungan langsung dalam model itu sendiri.

Tingkat verifikasi yang berbeda berlaku untuk bagian-bagian model yang berbeda. Tabel di bawah ini menjelaskan hierarki yang umum.

| Tingkat | Fokus | Kegiatan Khas |

|---|---|---|

| Verifikasi Unit | Blok/Attribut Individual | Konsistensi atribut, kendala parameter |

| Verifikasi Komponen | Subsistem | Kompatibilitas antarmuka, alur logika internal |

| Verifikasi Sistem | Arsitektur Lengkap | Kebutuhan end-to-end, simulasi skenario |

| Verifikasi Integrasi | Antarmuka Eksternal | Hardware dalam loop, stres lingkungan |

Bagaimana Anda tahu strategi berjalan dengan baik? Anda membutuhkan metrik kuantitatif. Metrik ini memberikan visibilitas terhadap kesehatan proyek dan kualitas model.

Bahkan dengan rencana yang jelas, organisasi menghadapi hambatan. Mengenali bahaya ini sejak dini memungkinkan mitigasi proaktif.

Membuat model rinci untuk area yang tidak krusial bagi fungsi inti sistem membuang waktu dan sumber daya. Fokuskan upaya verifikasi pada area berisiko tinggi dan kompleksitas tinggi.

Kebutuhan yang samar membuat verifikasi menjadi mustahil. Jika suatu kebutuhan menyatakan ‘Sistem harus merespons dengan cepat’, tidak ada metrik untuk diverifikasi. Kebutuhan harus dapat diukur dan tidak ambigu.

Menggunakan alat yang berbeda untuk kebutuhan, pemodelan, dan pengujian dapat mengganggu pelacakan. Pastikan ekosistem mendukung pertukaran data dan mempertahankan tautan sepanjang siklus hidup.

Otomasi sangat kuat, tetapi tidak dapat menggantikan penilaian manusia. Tinjauan oleh rekan kerja terhadap model sangat penting untuk menangkap kesalahan logis yang mungkin terlewat oleh skrip.

Verifikasi tidak boleh menjadi fase terpisah di akhir proyek. Harus diintegrasikan ke dalam siklus hidup pengembangan. Model V adalah kerangka kerja umum untuk integrasi ini.

| Sisi Kiri (Desain) | Pusat (Verifikasi) | Sisi Kanan (Implementasi) |

|---|---|---|

| Kebutuhan Sistem | Verifikasi Sistem | Integrasi Sistem |

| Arsitektur Sistem | Verifikasi Arsitektur | Integrasi Sistem |

| Desain Komponen | Verifikasi Komponen | Uji Komponen |

| Desain Modul | Verifikasi Modul | Uji Satuan |

Dengan menyelaraskan aktivitas verifikasi SysML dengan struktur ini, tim memastikan bahwa keputusan desain divalidasi sebelum kode atau perangkat keras diproduksi. Ini mengurangi biaya perbaikan secara signifikan.

Di luar pemeriksaan dasar, teknik lanjutan dapat memberikan wawasan yang lebih dalam mengenai perilaku sistem.

Diagram ini memungkinkan insinyur untuk memodelkan batasan fisik dan hubungan matematis. Mereka sangat penting untuk memverifikasi persyaratan kinerja seperti konsumsi daya, batas termal, atau toleransi tegangan. Menyelesaikan persamaan dalam diagram ini memberikan bukti bahwa desain memenuhi hukum fisika.

Untuk sistem dengan logika yang kompleks, Diagram Mesin Status sangat penting. Verifikasi di sini melibatkan pemeriksaan terhadap deadlock, keadaan yang tidak dapat diakses, dan logika transisi yang tepat. Ini memastikan sistem berperilaku dengan benar di bawah semua kondisi yang mungkin.

Tentukan kasus penggunaan yang mewakili penggunaan dunia nyata. Modelkan skenario-skenario ini dalam lingkungan SysML untuk melihat apakah sistem menanganinya sebagaimana yang diharapkan. Ini membantu mengungkap kasus-kasus tepi yang mungkin tidak muncul dalam pengujian fungsional standar.

Upaya verifikasi harus sebanding dengan risiko. Tidak semua persyaratan memiliki bobot yang sama. Persyaratan yang kritis terhadap keselamatan membutuhkan tingkat verifikasi yang lebih tinggi dibandingkan dengan persyaratan yang bersifat estetika.

Dengan memetakan risiko terhadap upaya verifikasi, tim dapat mengoptimalkan sumber daya sambil tetap menjaga standar keselamatan.

Sistem-sistem kritis misi sering kali hidup lebih lama dari tim yang membangun mereka. Artefak verifikasi harus dapat dipelihara. Ini berarti:

Menerapkan strategi verifikasi SysML merupakan perubahan budaya. Ini menggeser organisasi dari insinyur berbasis dokumen ke insinyur berbasis model. Transisi ini membutuhkan disiplin, pelatihan, dan komitmen terhadap kualitas. Namun, manfaatnya sangat besar: pengurangan risiko, biaya yang lebih rendah, dan kepercayaan diri yang lebih tinggi terhadap produk akhir.

Keberhasilan tergantung pada penerapan strategi secara konsisten. Ini bukan aktivitas sekali waktu, melainkan proses berkelanjutan yang berjalan sejalan dengan pengembangan. Dengan memasukkan verifikasi ke dalam setiap tahap alur kerja, organisasi dapat menghadirkan sistem kritis misi dengan keandalan yang mereka butuhkan.

Ingatlah bahwa model adalah alat komunikasi sebanyak alat spesifikasi. Model yang telah diverifikasi adalah pemahaman yang telah diverifikasi terhadap sistem. Pemahaman bersama ini adalah dasar dari pengiriman sistem yang sukses.