Visual Paradigm Desktop |

Visual Paradigm Desktop |  Visual Paradigm Online

Visual Paradigm OnlineSistem rekayasa modern tidak lagi merupakan kumpulan bagian yang terisolasi. Mereka adalah ekosistem yang kompleks di mana rekayasa mekanik, listrik, perangkat lunak, dan sistem bersatu. Keterpaduan ini menciptakan tantangan: bagaimana tim yang beragam dapat berbicara dalam bahasa yang sama sambil mempertahankan keahlian khusus mereka? Bahasa Pemodelan Sistem (SysML) menawarkan pendekatan terstruktur, tetapi penyesuaian antar domain membutuhkan pola yang disengaja. Panduan ini menguraikan strategi penting untuk mengintegrasikan tim rekayasa yang beragam menggunakan prinsip rekayasa sistem berbasis model. Kami fokus pada mekanisme penyesuaian praktis yang mengurangi gesekan dan meningkatkan pelacakan tanpa bergantung pada fitur alat khusus.

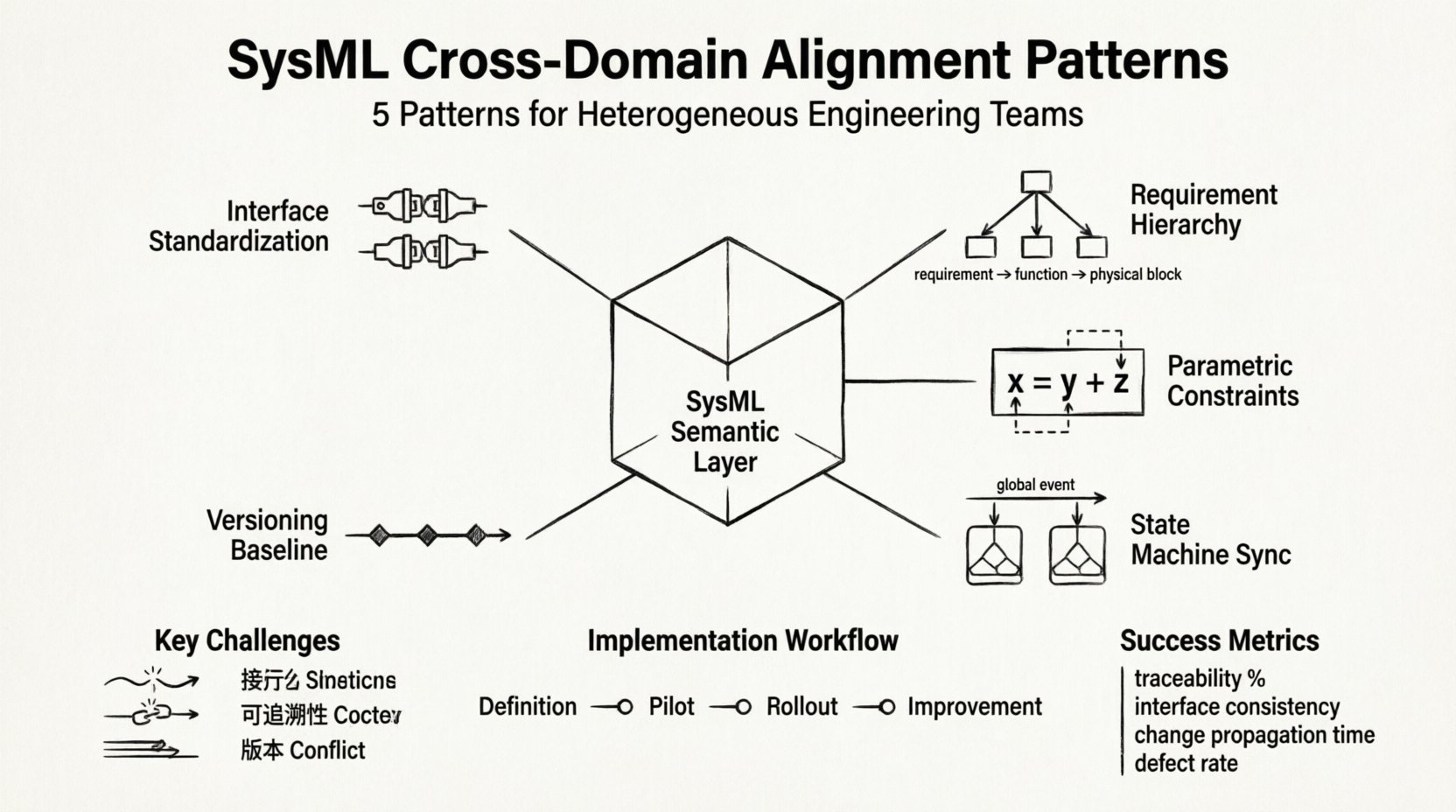

Tim yang beragam beroperasi dengan model mental, terminologi, dan ekspektasi siklus hidup yang berbeda. Seorang insinyur perangkat lunak berpikir dalam algoritma dan alur logika. Seorang insinyur mekanik berpikir dalam toleransi dan bahan. Seorang insinyur sistem berpikir dalam persyaratan dan antarmuka. Ketika pandangan-pandangan ini bertabrakan tanpa metode integrasi terstruktur, kesalahan menyebar terlambat dalam siklus hidup. SysML berfungsi sebagai lapisan semantik bersama, tetapi pemodelan mentah tidak cukup. Kita membutuhkan pola khusus untuk memastikan bahwa definisi dalam satu domain dipetakan dengan benar ke domain lain.

Tanpa penyesuaian, masalah-masalah berikut sering muncul:

Untuk mengurangi risiko ini, kita harus menerapkan pola penyesuaian yang menstandarkan cara informasi ditukar antar disiplin. Pola-pola ini bukan tentang memaksakan satu alat saja; mereka tentang menentukan kontrak pemodelan yang konsisten.

Titik kontak paling kritis antar domain adalah antarmuka. Antarmuka yang salah dipahami merupakan penyebab utama penundaan integrasi. Dalam SysML, ini dikelola melalui Diagram Definisi Blok (BDD) dan Diagram Blok Internal (IBD). Pola ini melibatkan aturan ketat tentang bagaimana port dan port aliran didefinisikan dan dikonsumsi.

Ketika tim perangkat keras mendefinisikan bus daya, tim perangkat lunak harus mengonsumsi definisi yang persis sama. Pola ini mengharuskan proses tinjauan di mana definisi antarmuka disetujui oleh semua domain yang mengonsumsi sebelum tahap desain dilanjutkan. Ini menciptakan kontrak yang tidak tergantung pada alat perangkat lunak tertentu.

Persyaratan adalah sumber kebenaran tentang apa yang harus dilakukan sistem. Namun, persyaratan sering berada di satu repositori sementara model berada di repositori lain. Pola penyesuaian ini berfokus pada bagaimana persyaratan didekomposisi menjadi blok fungsional dan fisik.

Untuk tim yang heterogen, hierarki ini berfungsi sebagai jembatan. Tim perangkat lunak memetakan modul kode ke blok fungsional. Tim perangkat keras memetakan komponen ke blok fisik. Kedua tim harus dapat dilacak kembali ke simpul kebutuhan yang sama. Ini menciptakan pandangan terpadu mengenai cakupan di berbagai disiplin ilmu.

Analisis rekayasa sering membutuhkan kendala matematis. Batas kinerja, massa, daya, dan termal sangat penting di seluruh bidang. Diagram Parametrik SysML menyediakan mekanisme untuk berbagi kendala-kendala ini. Tantangannya adalah memastikan bahwa parameter yang didefinisikan dalam model konsisten dengan alat analisis yang digunakan oleh tim tertentu.

Ketika tim mekanik menentukan kendala massa, tim listrik harus dapat merujuk variabel tersebut dalam anggaran daya mereka. Pola ini menjamin bahwa studi pertukaran dilakukan berdasarkan data yang konsisten. Ini mencegah terjadinya skenario di mana tim perangkat lunak mengoptimalkan kinerja sementara tim perangkat keras mengoptimalkan biaya, yang menghasilkan sistem yang tidak seimbang.

Pemodelan perilaku sering menjadi tempat yang paling membingungkan. Mesin status menggambarkan logika sistem. Insinyur perangkat lunak sering menggunakan UML atau diagram status berbasis kode, sementara insinyur sistem menggunakan SysML. Menyelaraskan pandangan ini sangat penting untuk memahami dinamika sistem.

Pola ini sangat berguna untuk sistem tertanam di mana batas antara logika firmware dan perangkat keras menjadi kabur. Dengan menyinkronkan mesin status, tim dapat memverifikasi bahwa sistem merespons dengan benar terhadap semua input sepanjang siklus hidupnya.

Model berkembang. Perubahan di satu domain dapat membuat asumsi di domain lain menjadi tidak valid. Mengelola perkembangan ini membutuhkan strategi penomoran versi yang kuat. Pola ini berfokus pada bagaimana basis dibuat dan bagaimana perubahan disebarkan.

Versi yang efektif memastikan bahwa tim dapat kembali ke status stabil jika perubahan menyebabkan masalah integrasi. Ini juga memungkinkan aliran pengembangan paralel di mana tim dapat bekerja pada fitur yang berbeda tanpa saling menghambat.

Bahkan dengan pola-pola tersebut, tantangan tetap ada. Tabel berikut menjelaskan titik gesekan umum dan strategi penyelarasan yang sesuai.

| Tantangan | Penyebab Utama | Pola Penyelarasan SysML |

|---|---|---|

| Perpindahan Persyaratan | Persyaratan diperbarui secara terpisah | Paket Persyaratan Terpusat dengan Gerbang Tinjauan |

| Ketidaksesuaian Antarmuka | Jenis port tidak distandarkan | Pola Standarisasi Definisi Antarmuka |

| Kerusakan Jejak Kembali | Tautan hilang selama migrasi | Pola Hierarki Dekomposisi Persyaratan |

| Ketidakkonsistenan Analisis | Definisi parameter yang berbeda | Pola Berbagi Kendala Parametrik |

| Kerancuan Perilaku | Definisi acara lokal | Pola Sinkronisasi Mesin Status |

Mengadopsi pola-pola ini memerlukan perubahan dalam alur kerja. Ini bukan hanya tentang mengubah model; ini tentang mengubah proses kolaborasi. Langkah-langkah berikut menjelaskan jalur implementasi yang umum.

Pola-pola saja tidak menjamin kualitas. Tata kelola memastikan bahwa pola-pola tersebut diikuti. Ini melibatkan tinjauan model secara rutin dan audit. Tujuannya adalah menjaga integritas model sebagai satu-satunya sumber kebenaran.

Jaminan kualitas sebaiknya diotomasi sebisa mungkin. Skrip dapat memeriksa kebutuhan yang terpisah atau jenis antarmuka yang hilang. Ini mengurangi beban manual bagi insinyur dan memungkinkan mereka fokus pada desain.

Bagaimana Anda tahu pola keselarasan berjalan dengan baik? Anda membutuhkan metrik. Indikator kinerja utama (KPI) berikut membantu mengukur efektivitas strategi keselarasan.

Melacak metrik-metrik ini seiring waktu memberikan wawasan apakah tim sedang bergerak menuju keterpaduan yang lebih baik. Penurunan tingkat kesalahan dan peningkatan cakupan menunjukkan keberhasilan. Jika metrik stagnan, pola-pola tersebut mungkin perlu disesuaikan.

Tim yang heterogen sering menggunakan alat yang berbeda. Beberapa mungkin lebih suka standar terbuka, sementara yang lain mengandalkan ekosistem tertentu. Pola keterpaduan ini berfokus pada pertukaran data daripada keseragaman alat.

Tujuannya adalah memastikan data tetap valid terlepas dari alat apa yang digunakan untuk melihatnya. Ini mencegah terjebak pada satu pemasok dan memungkinkan tim memilih alat terbaik untuk domain spesifik mereka.

Menyelaraskan tim rekayasa yang heterogen adalah proses berkelanjutan. Ini membutuhkan disiplin, komunikasi, dan komitmen bersama terhadap model sebagai artefak utama. Pola-pola yang diuraikan di sini memberikan kerangka kerja untuk mencapai keterpaduan ini tanpa mengharuskan penggunaan tumpukan teknologi tertentu. Dengan fokus pada antarmuka, persyaratan, batasan, dan perilaku, tim dapat mengurangi gesekan dan meningkatkan kualitas sistem.

Keberhasilan dalam keterpaduan SysML berasal dari konsistensi. Ketika setiap tim mengikuti aturan yang sama dalam mendefinisikan antarmuka dan melacak persyaratan, kompleksitas sistem menjadi terkelola. Pendekatan ini memungkinkan tim untuk memperluas upaya rekayasa mereka sambil tetap menjaga kendali atas arsitektur sistem.

Mulai kecil. Pilih satu pola dan terapkan pada satu subsistem. Ukur hasilnya. Kemudian perluas. Pendekatan iteratif ini memungkinkan tim menyesuaikan pola-pola tersebut dengan konteks spesifik mereka sambil tetap mempertahankan prinsip inti keterpaduan dan pelacakan.