Visual Paradigm Desktop |

Visual Paradigm Desktop |  Visual Paradigm Online

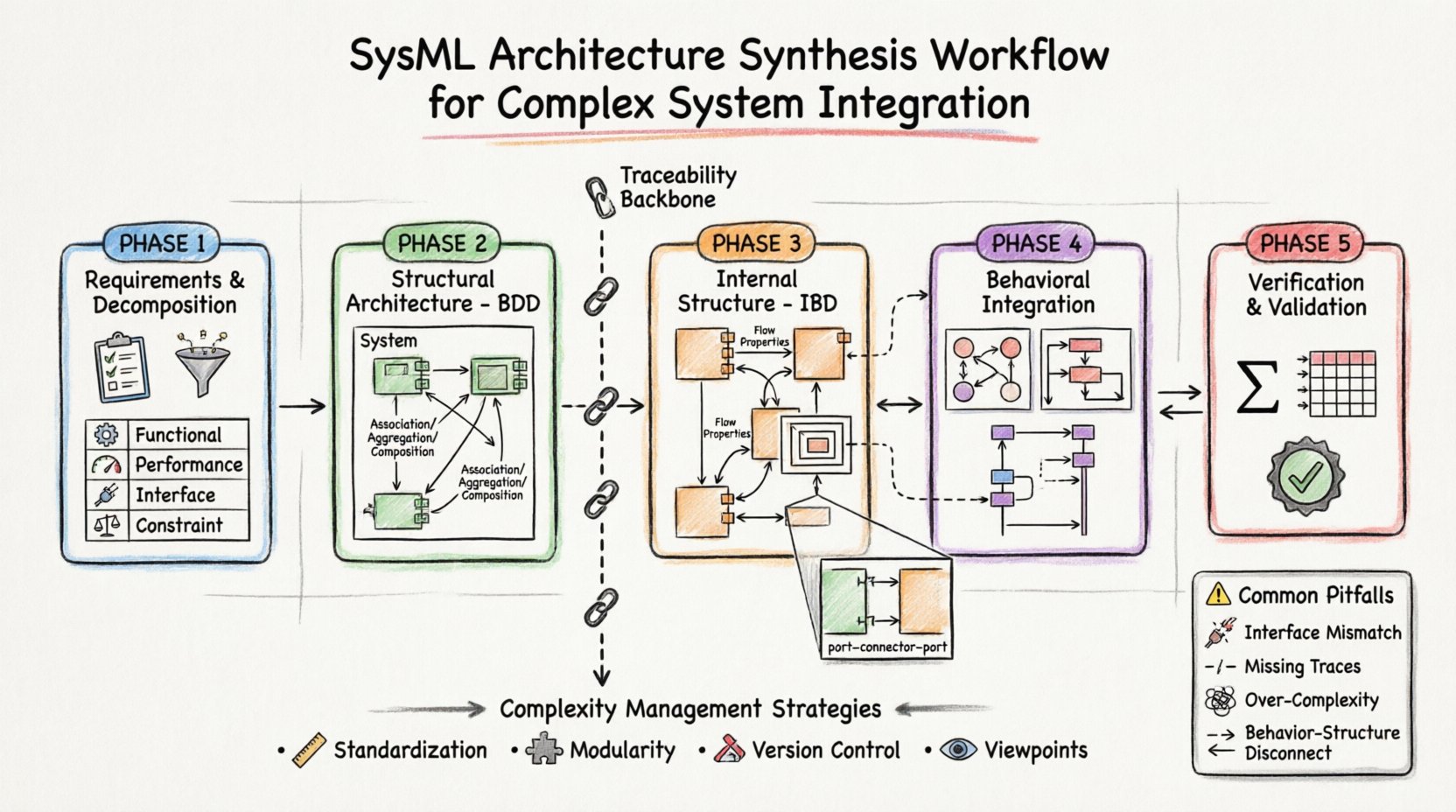

Visual Paradigm OnlineMengembangkan sistem yang kompleks membutuhkan pendekatan terstruktur untuk mengelola kompleksitas yang terus meningkat. Seiring sistem berkembang dalam cakupan, meliputi berbagai bidang dan disiplin ilmu, metode dokumentasi tradisional sering kali gagal mempertahankan konsistensi. Teknik Rekayasa Sistem Berbasis Model (MBSE) menangani tantangan ini dengan menciptakan duplikat digital dari arsitektur sistem. Dalam kerangka ini, Bahasa Pemodelan Sistem (SysML) menyediakan sintaks standar untuk menggambarkan struktur sistem, perilaku, dan batasan. Panduan ini menjelaskan alur kerja sintesis arsitektur, dengan fokus pada cara mengintegrasikan sub-sistem yang berbeda menjadi satu kesatuan yang utuh menggunakan teknik pemodelan yang ketat.

Sintesis arsitektur bukan sekadar menggambar diagram; ini adalah proses logis yang mendefinisikan bagaimana komponen saling berinteraksi untuk memenuhi kebutuhan tingkat tinggi. Proses ini menuntut ketepatan dalam mendefinisikan antarmuka, mengalokasikan fungsi, dan memastikan pelacakan dari konsep hingga implementasi. Bagian-bagian berikutnya menjelajahi fase-fase alur kerja, representasi diagramatik, serta strategi untuk mempertahankan integritas sepanjang siklus pengembangan.

Sebelum memulai sintesis, seseorang harus memahami tujuan inti dari model ini. Tujuannya adalah mengurangi ambiguitas dan risiko sebelum prototipe fisik dibuat. Dalam skenario integrasi yang kompleks, banyak tim sering bekerja pada sub-sistem yang berbeda secara bersamaan. Model arsitektur bersama berfungsi sebagai satu-satunya sumber kebenaran. Konteks bersama ini memastikan bahwa perubahan di satu area segera tercermin di semua tampilan terkait.

Alur kerja sintesis bergantung pada beberapa prinsip utama:

Tanpa prinsip-prinsip ini, model menjadi kumpulan diagram yang terpisah. Alur kerja sintesis menghubungkan mereka menjadi narasi logis yang menggambarkan operasi sistem.

Proses sintesis dimulai dari kebutuhan. Arsitektur yang kuat tidak dapat disintesis dari kebutuhan yang samar atau tidak lengkap. Kegiatan utama dalam fase ini melibatkan penyempurnaan kebutuhan tingkat tinggi dari pemangku kepentingan menjadi kebutuhan teknis. Ini sering direpresentasikan menggunakan diagram Kebutuhan dalam SysML.

Kegiatan kunci selama fase ini meliputi:

Sangat penting untuk membedakan antara kebutuhan pengguna dan kebutuhan rekayasa. Kebutuhan pengguna menggambarkan apa yang harus dicapai sistem dari sudut pandang operasional. Kebutuhan rekayasa mendefinisikan spesifikasi teknis yang diperlukan untuk memenuhi kebutuhan tersebut. Alur kerja sintesis menutup celah ini dengan mengalokasikan kebutuhan rekayasa ini ke blok sistem tertentu.

| Jenis Kebutuhan | Fokus | Contoh |

|---|---|---|

| Fungsional | Apa yang dilakukan sistem | Sistem harus memproses 1000 paket per detik. |

| Kinerja | Seberapa baik kinerjanya | Latensi harus di bawah 50ms. |

| Antarmuka | Bagaimana koneksi dilakukan | Harus menggunakan protokol ISO-8859-1. |

| Kendala | Keterbatasan | Berat tidak boleh melebihi 5kg. |

Pemecahan yang tepat memastikan tidak ada persyaratan yang ditinggalkan tanpa penanganan. Setiap persyaratan harus dapat dilacak ke setidaknya satu elemen desain. Jika suatu persyaratan tidak dapat dialokasikan, hal ini menunjukkan adanya celah dalam arsitektur yang harus ditangani sebelum melanjutkan.

Setelah persyaratan ditentukan, arsitektur struktural dikembangkan menggunakan Diagram Definisi Blok (BDD). Blok adalah unit dasar struktur dalam SysML. Blok mewakili komponen sistem, yang dapat berupa bagian tunggal atau gabungan dari bagian-bagian lain.

Proses sintesis dalam BDD melibatkan:

Ketika mendefinisikan blok, sangat penting untuk memisahkan antarmuka dari implementasi. Antarmuka menentukan apa yang dibuka oleh blok ke dunia luar. Implementasi menentukan bagaimana blok mencapai fungsinya. Pemisahan ini memungkinkan fleksibilitas; logika internal suatu subsistem dapat berubah tanpa memengaruhi bagian lain dari arsitektur, selama antarmuka tetap konstan.

Hubungan antar blok sangat penting untuk sintesis. Hubungan Asosiasi menunjukkan koneksi. Hubungan Agregasi menunjukkan hubungan seluruh-bagian di mana bagian dapat ada secara mandiri. Hubungan Komposisi menunjukkan ketergantungan siklus hidup yang kuat. Memilih jenis hubungan yang tepat memastikan model secara akurat mencerminkan realitas fisik sistem.

Sementara BDD mendefinisikan bagian-bagian, Diagram Blok Internal (IBD) mendefinisikan bagaimana bagian-bagian tersebut dihubungkan. Ini adalah inti dari alur kerja integrasi. IBD menunjukkan struktur internal dari suatu blok tertentu, mengungkap aliran informasi dan material antar komponennya.

Elemen-elemen kunci dalam IBD meliputi:

Selama sintesis, arsitek harus memastikan bahwa setiap interaksi yang diperlukan diwakili oleh konektor. Konektor yang hilang sering menunjukkan celah integrasi. Selain itu, arah aliran data harus jelas. SysML membedakan antara arah aliran dan arah referensi. Mengaburkan keduanya dapat menyebabkan kesalahan logis pada tahap simulasi atau analisis.

Tantangan umum dalam sintesis IBD adalah mengelola kompleksitas. Seiring bertambahnya jumlah blok, diagram dapat menjadi berantakan. Untuk mengurangi hal ini, arsitek sebaiknya menggunakan IBD bersarang. Ini memungkinkan penyembunyian detail internal suatu subsistem sambil tetap mempertahankan tampilan sistem tingkat atas. Pendekatan hierarkis ini menjaga model tetap terkelola dengan baik dan mudah dibaca.

Struktur saja tidak menjelaskan bagaimana sistem berperilaku. Alur kerja sintesis harus mengintegrasikan model perilaku untuk memastikan sistem beroperasi dengan benar seiring waktu. SysML menawarkan beberapa jenis diagram untuk perilaku, termasuk Diagram Mesin Status, Diagram Aktivitas, dan Diagram Urutan.

Proses integrasi melibatkan pemetaan elemen-elemen struktural ke peristiwa perilaku. Sebagai contoh, port tertentu pada suatu blok bisa memicu transisi status. Diagram aktivitas bisa menjelaskan logika yang dieksekusi saat data mengalir melalui suatu konektor.

Kegiatan kunci dalam fase ini meliputi:

Sangat penting untuk memastikan konsistensi antara struktur dan perilaku. Jika suatu port didefinisikan dalam IBD tetapi tidak pernah digunakan dalam Mesin Status, maka itu mewakili kode mati atau antarmuka yang tidak digunakan. Sebaliknya, jika suatu perilaku membutuhkan port yang tidak ada dalam struktur, maka model tersebut tidak lengkap. Alur kerja sintesis harus secara iteratif memeriksa keselarasan ini.

| Jenis Diagram | Kasus Penggunaan Utama | Fokus Integrasi |

|---|---|---|

| Mesin Status | Logika Kontrol | Peristiwa pemicu dari port |

| Aktivitas | Logika Proses | Aliran data dan kontrol |

| Urutan | Urutan Waktu | Waktu pertukaran pesan |

Dengan menghubungkan perilaku ke struktur, model menjadi artefak siap simulasi. Ini memungkinkan insinyur menguji logika sebelum komponen fisik tersedia. Hal ini mengurangi risiko menemukan kesalahan integrasi di akhir siklus pengembangan.

Sintesis tidak selesai hingga arsitektur divalidasi terhadap persyaratan. Verifikasi bertanya: ‘Apakah kita membangun sistem dengan benar?’ Validasi bertanya: ‘Apakah kita membangun sistem yang tepat?’ SysML mendukung hal ini melalui Diagram Parametrik dan Blok Kendala.

Diagram Parametrik memungkinkan definisi persamaan dan hubungan antar parameter. Ini sangat penting untuk analisis kinerja. Misalnya, jika sebuah subsistem memiliki persyaratan konsumsi daya, model parametrik dapat menghitung apakah blok pasokan daya memenuhi permintaan tersebut berdasarkan persyaratan beban.

Validasi sering dicapai melalui matriks pelacakan. Matriks pelacakan menghubungkan persyaratan dengan elemen desain dan aktivitas verifikasi. Jika suatu persyaratan tidak dapat diverifikasi, maka tetap tidak divalidasi. Alur kerja sintesis harus memastikan setiap persyaratan memiliki jalur verifikasi yang sesuai.

Kegiatan verifikasi umum meliputi:

Seiring sistem tumbuh, jumlah elemen model meningkat secara eksponensial. Mengelola kompleksitas ini merupakan tantangan utama dalam sintesis arsitektur. Tanpa disiplin ketat, model menjadi tidak terkelola. Strategi-strategi berikut membantu menjaga kendali:

Pelacakan adalah tulang punggung integrasi. Ini memastikan perubahan pada persyaratan menyebar ke desain. Dalam sistem yang kompleks, perubahan pada satu subsistem dapat menyebar ke seluruh arsitektur. Pemeriksaan pelacakan otomatis dapat mengidentifikasi dampak ini dengan cepat. Ini mencegah rekayasa ‘silos’ di mana satu tim mengubah parameter tanpa menyadari bahwa hal itu merusak desain tim lain.

Bahkan dengan alur kerja yang telah ditentukan, masih terdapat jebakan. Mengenali mereka sejak dini dapat menghemat waktu dan sumber daya yang signifikan. Berikut ini adalah masalah umum yang dihadapi selama sintesis SysML.

| Jebakan | Konsekuensi | Strategi Pengurangan Dampak |

|---|---|---|

| Ketidaksesuaian Antarmuka | Kerusakan data atau kegagalan | Tentukan tipe data yang ketat pada port |

| Jejak yang Hilang | Persyaratan yang Tidak Diverifikasi | Terapkan aturan pelacakan |

| Terlalu Kompleks | Model menjadi tidak dapat dibaca | Gunakan dekomposisi hierarkis |

| Kesenjangan Antara Perilaku dan Struktur | Kesalahan simulasi | Ulas IBD dan Mesin Status bersamaan |

Masalah lain yang sering muncul adalah upaya integrasi ‘big bang’. Mencoba menghubungkan semua subsistem pada akhir proyek sangat berisiko. Alur kerja sintesis mendorong integrasi bertahap. Subsistem harus diintegrasikan dan diverifikasi secara bertahap. Ini membatasi masalah pada subsistem tertentu, bukan seluruh arsitektur.

Sama seperti kode membutuhkan pengujian, model juga membutuhkan jaminan kualitas. Ini melibatkan pemeriksaan model terhadap kesalahan sintaksis, konsistensi logis, dan kelengkapan. Pemeriksaan otomatis sering tersedia dalam lingkungan pemodelan. Pemeriksaan ini dapat memverifikasi bahwa semua port terhubung, semua persyaratan dilacak, dan semua parameter didefinisikan.

Ulasan manual juga diperlukan. Ulasan oleh rekan kerja terhadap arsitektur dapat menangkap kesalahan logis yang terlewat oleh alat otomatis. Peninjau harus fokus pada kejelasan desain dan ketahanan antarmuka. Mereka harus bertanya: ‘Jika komponen ini gagal, apakah sistem akan mengalami penurunan secara halus?’ Pertanyaan jenis ini mendorong ketahanan ke dalam arsitektur.

Bidang pemodelan sistem terus berkembang. Tren yang muncul berfokus pada peningkatan otomatisasi dan interoperabilitas. Kemampuan untuk bertukar model antar alat menjadi semakin krusial. Standar terbuka memastikan bahwa alur kerja sintesis arsitektur tidak tergantung pada satu pemasok saja.

Selain itu, integrasi alat simulasi langsung ke dalam lingkungan pemodelan sedang meningkatkan akurasi analisis. Ini memungkinkan prediksi yang lebih akurat terhadap kinerja sistem sebelum realisasi fisik. Alur kerja sintesis harus beradaptasi terhadap alat-alat ini, memastikan bahwa model tetap menjadi acuan utama meskipun kemampuan simulasi berkembang.

Pada akhirnya, tujuan dari alur kerja sintesis arsitektur adalah menghasilkan sistem yang berfungsi sesuai harapan. Dengan mengikuti proses yang terdisiplin, memanfaatkan seluruh kekuatan SysML, dan mempertahankan standar kualitas yang ketat, tim rekayasa dapat mengelola kompleksitas dan menghasilkan solusi bernilai tinggi. Model berfungsi sebagai gambaran kerja untuk kesuksesan, membimbing integrasi dari konsep menuju kenyataan.